1. Úvod

Krystalových oscilátorů generují vysoce stabilní hodinové signály, které jsou potřebné téměř ve všech elektronických systémech – od jednoduchých obvodů mikrokontrolérů až po vysokorychlostní systémy přenosu dat.

Výstupní signál oscilátoru musí být kompatibilní s následující logickou rodinou nebo rozhraním. V průběhu desetiletí se vyvinuly různé výstupní standardy, každý přizpůsobený požadavkům své doby a aplikace.

Tento dokument poskytuje komplexní přehled sedmi nejběžnějších typů výstupních signálů v krystalových oscilátorech: CMOS, TTL, ořezaná sinusová vlna, sinusový signál, LVPECL, LVDS a HCSL.

Pro každý typ jsou popsány historický vývoj, elektrické vlastnosti, typický tvar signálu a preferované oblasti použití.

2. Historický vývoj

Vývoj typů výstupních signálů je úzce spojen s evolucí polovodičové technologie a rostoucími požadavky na hodinové frekvence a integritu signálu:

2.1 TTL (tranzistorově-tranzistorová logika) – od cca 1964

TTL byl jedním z prvních široce rozšířených standardů digitální logiky a byl zaveden firmou Texas Instruments jako řada 7400. Oscilátory s výstupem TTL pracují s napájecím napětím 5 V a poskytují rozsahy úrovní přímo kompatibilní s hradly TTL. Standard formoval digitální elektroniku po desetiletí a byl dominantním logickým standardem až do 90. let.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – od cca 1968

Technologie CMOS byla původně vyvinuta pro RCA a vyznačuje se extrémně nízkou klidovou spotřebou proudu. Oscilátory CMOS poskytují výstupní signály typu rail-to-rail, což znamená, že výstup osciluje téměř výhradně mezi 0 V a VCC. S pokračující miniaturizací a trendem směrem k nižším napájecím napětím (3,3 V, 2,5 V, 1,8 V) se CMOS stala nejrozšířenějším výstupním standardem pro krystalové oscilátory.

2.3 Sinus – od počátků techniky oscilátorů

Sinusové výstupní signály jsou staré jako samotná technologie oscilátorů. Krystalové oscilátory fyzicky kmitají sinusoidně; všechny ostatní tvary signálů jsou generovány následnými obvody. Sinusové výstupy jsou upřednostňovány ve vysokofrekvenční technologii, měřicích přístrojích a zpracování analogových signálů, protože negenerují harmonické.

2.4 Clipped Sine Wave – od cca 70. let

Výstup Clipped Sine Wave představuje kompromis mezi sinusovým a obdélníkovým výstupem. Sinusový signál je na špičkách omezen (oříznut), čímž vznikají strmější hrany než u čistého sinusu, ale méně harmonických než u obdélníkového signálu. Tento typ výstupu nalezl uplatnění zejména v telekomunikacích a ve starších vysokofrekvenčních aplikacích. Obvody Clipped Sine Wave se dnes používají především ještě v TCXO. S touto technologií lze stavat výrazně úspornější TCXO než s technologií CMOS. CSW-TCXO se proto používají jako reference v navigačních zařízeních, tisňových systémech a branach. Všude tam, kde je potřeba dosah signálu (rádio) a velmi přesné polohování.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – od cca 90. let

S potřebou stále vyšších hodinových frekvencí v síťových a telekomunikačních systémech vznikl LVPECL jako rychlá diferenční výstupní logika. LVPECL je založen na klasické technice ECL (Emitter-Coupled Logic), vyvinuté již v 60. letech pro vysokořychlostní aplikace, a adaptuje ji pro nižší napájecí napětí (3,3 V místo -5,2 V). LVPECL nabízí extrémně krátké přepínací časy a je vhodný pro frekvence výrazně nad 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – od 1994

LVDS byl zaveden v roce 1994 jako standard ANSI/TIA/EIA-644 a optimalizuje diferenční přenos signálu pro nízkou spotřebu a vysoké přenosové rychlosti. Malý diferenční napěťový zdvih pouhých 350 mV umožňuje rychlé přepínání při minimální elektromagnetické emisi. LVDS je dnes široce rozšířen v rozhraních displejů, sériových datových linkách a taktování FPGA.

2.7 HCSL (High-Speed Current Steering Logic) – od cca 2002

HCSL byl vyvinut speciálně pro standard PCI Express a od první generace PCIe je standardem referenčních hodin. PCI-SIG specifikoval HCSL jako proudově řízený diferenční signál s velmi nízkým napěťovým zdvihem, optimalizovaný pro referenční hodiny 100 MHz v systémech PCIe. HCSL je dnes nepostradatelný v každém PC, serveru a vestavěném systému s rozhraním PCIe.

3. Přehled tvarů signálů

Následující diagramy ukazují idealizované průběhy signálů sedmi typů výstupů. Všimněte si různých rozsahů napětí a zdvihů signálu – ty jsou rozhodující pro kompatibilitu s následnými přijímači.

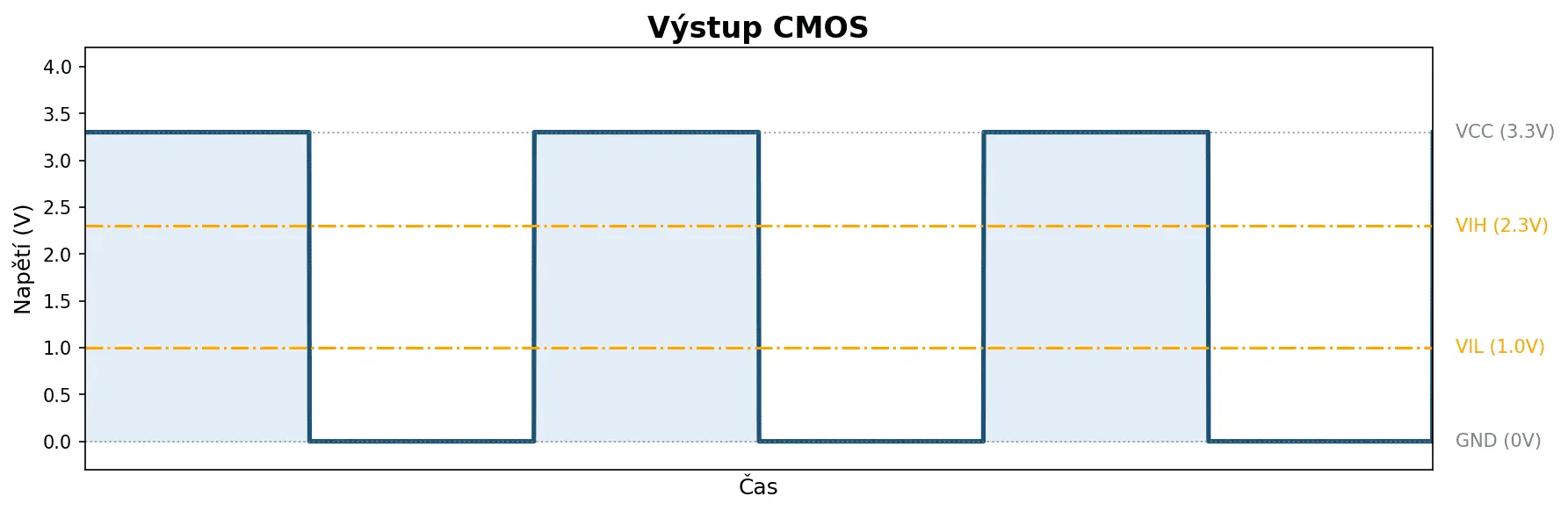

3.1 CMOS

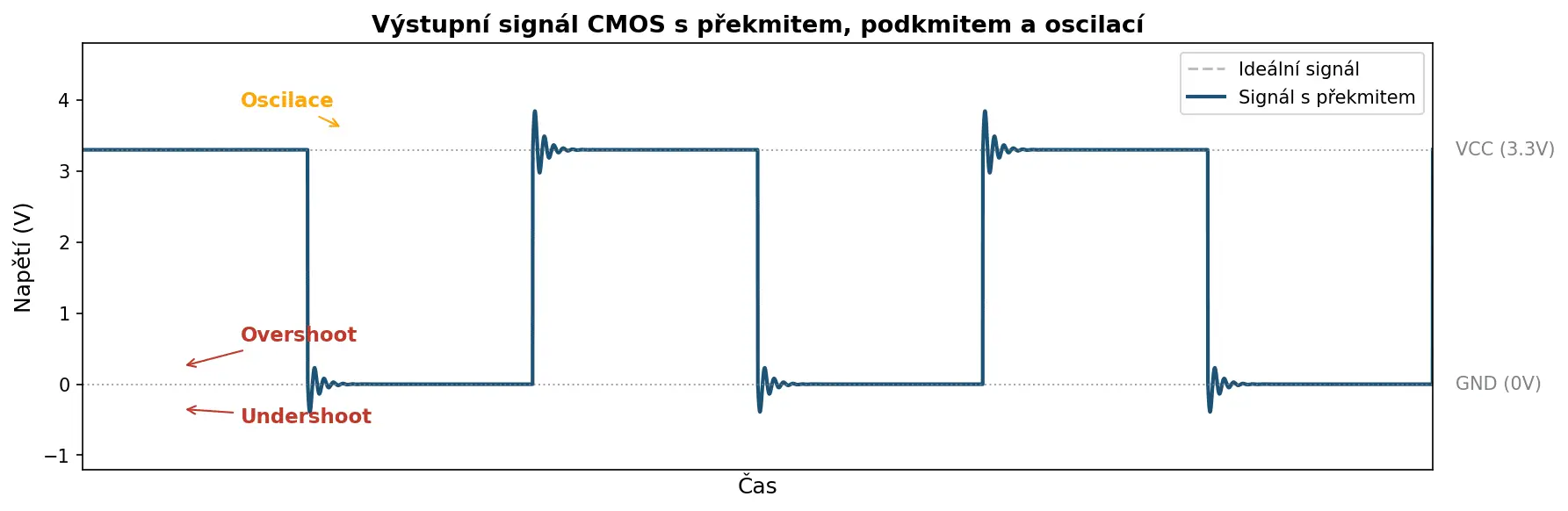

Obr. 1: Výstupní signál CMOS – obdélníkový signál rail-to-rail mezi 0 V a VCC (zde 3,3 V)

Signál CMOS se vyznačuje úplným napěťovým zdvihem mezi GND a VCC. Vstupní prahy VIL a VIH leží typicky při 30 % resp. 70 % VCC, což zaručuje širokou odolnost proti rušení. Symetrické struktury výstupního budice (MOSFET kanálu P/kanálu N) umožňují téměř stejné časy náběhu a sestupu.

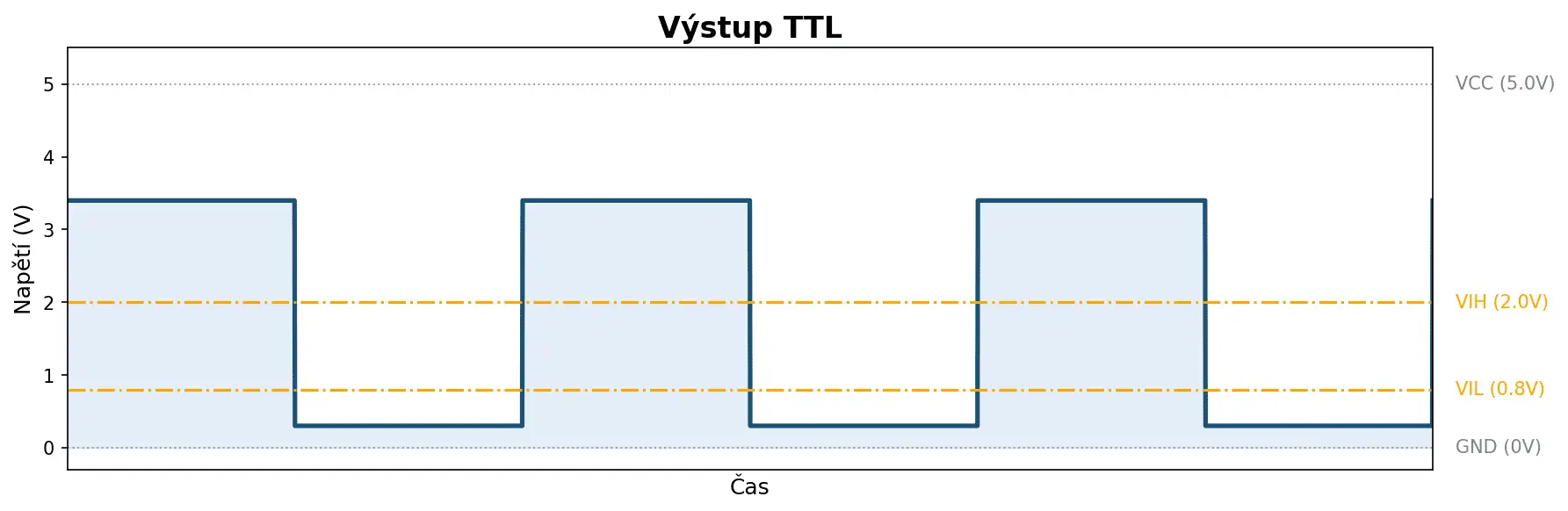

3.2 TTL

Obr. 2: Výstupní signál TTL – VOH typicky 3,4 V, VOL typicky 0,3 V při napájení 5 V

Na rozdíl od výstupu CMOS nedosahuje TTL úrovní rail-to-rail. Vysoká úroveň (VOH) leží typicky při 3,4 V (minimálně 2,4 V), nízká úroveň (VOL) při maximálně 0,4 V. Asymetrické prahy (VIL = 0,8 V, VIH = 2,0 V) vyplývají z bipolární tranzistorové architektury. Tzv. „zakázaná zóna“ mezi 0,8 V a 2,0 V nesmí být ve statickém provozu zaujímána.

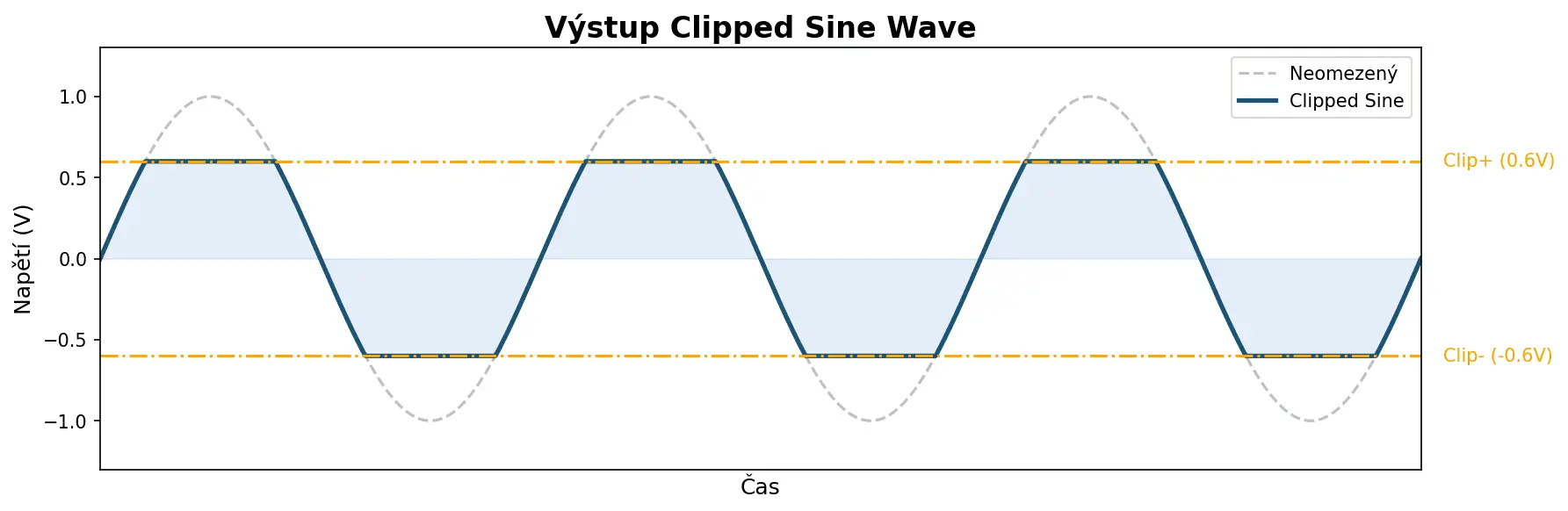

3.3 Oříznutá sinusová vlna

Obr. 3: Výstup Clipped Sine Wave – sinusový signál s omezenými amplitudovými špičkami

U výstupu Clipped Sine Wave je přirozený sinusový signál krystalového rezonátoru omezen na definovaných prahových hodnotách. Přerušovaná čára ukazuje neomezený sinusový průběh. Díky oříznutí vznikají strmější průchody nulou než u čistého sinusu, což usnadňuje buzení následné logiky, přičemž obsah harmonických zůstává umírněný.

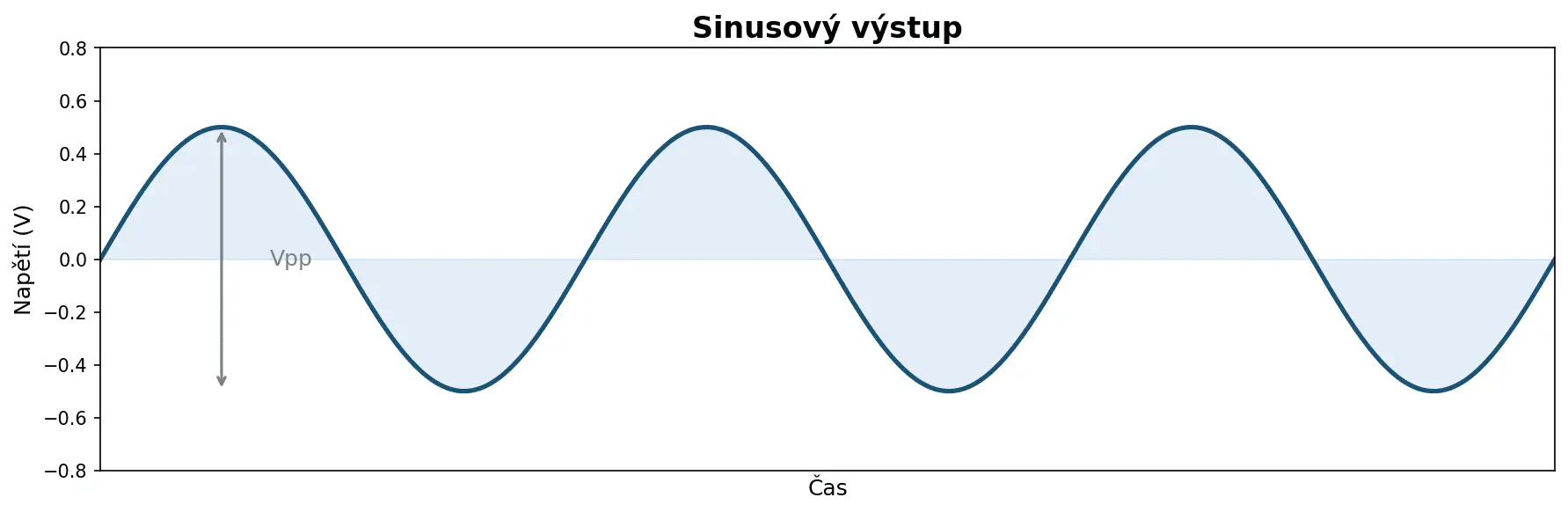

3.4 Sinus

Obr. 4: Sinusový výstup – čistý sinusový signál s definovaným napětím špička-špička (Vpp)

Sinusový výstup poskytuje nejčistší spektrum ze všech výstupních forem: ideálně pouze jednu jedinou spektrální čáru na základní frekvenci. Amplituda se udává jako napětí špička-špička (Vpp) nebo jako výkon v dBm. Typické hodnoty jsou 0,5 až 1,0 Vpp nebo 0 až +13 dBm v systémech 50 Ω.

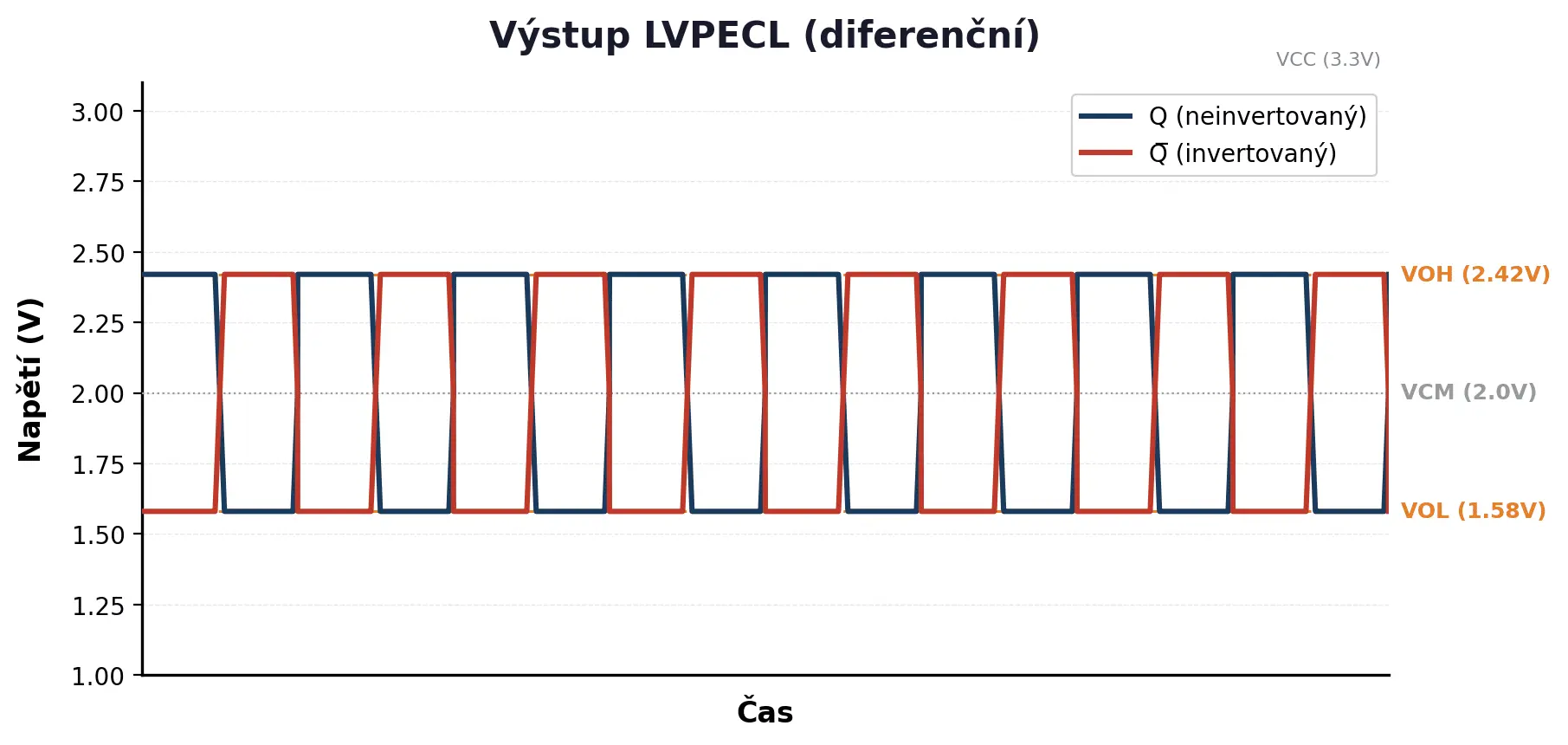

3.5 LVPECL

Obr. 5: Výstup LVPECL – diferenční signál s cca 800 mV celkového zdvihu kolem VCC–1,3 V

LVPECL používá diferenční vedení signálu: dva komplementární výstupy (Q a Q̅) přepínají v protifázi kolem společné souhlasné úrovně (VCM), typicky při VCC–1,3 V. Diferenční napěťový zdvih činí cca 800 mV. Architektura proudového zdroje umožňuje extrémně rychlé přepínací časy s minimální tendencí k překmitům.

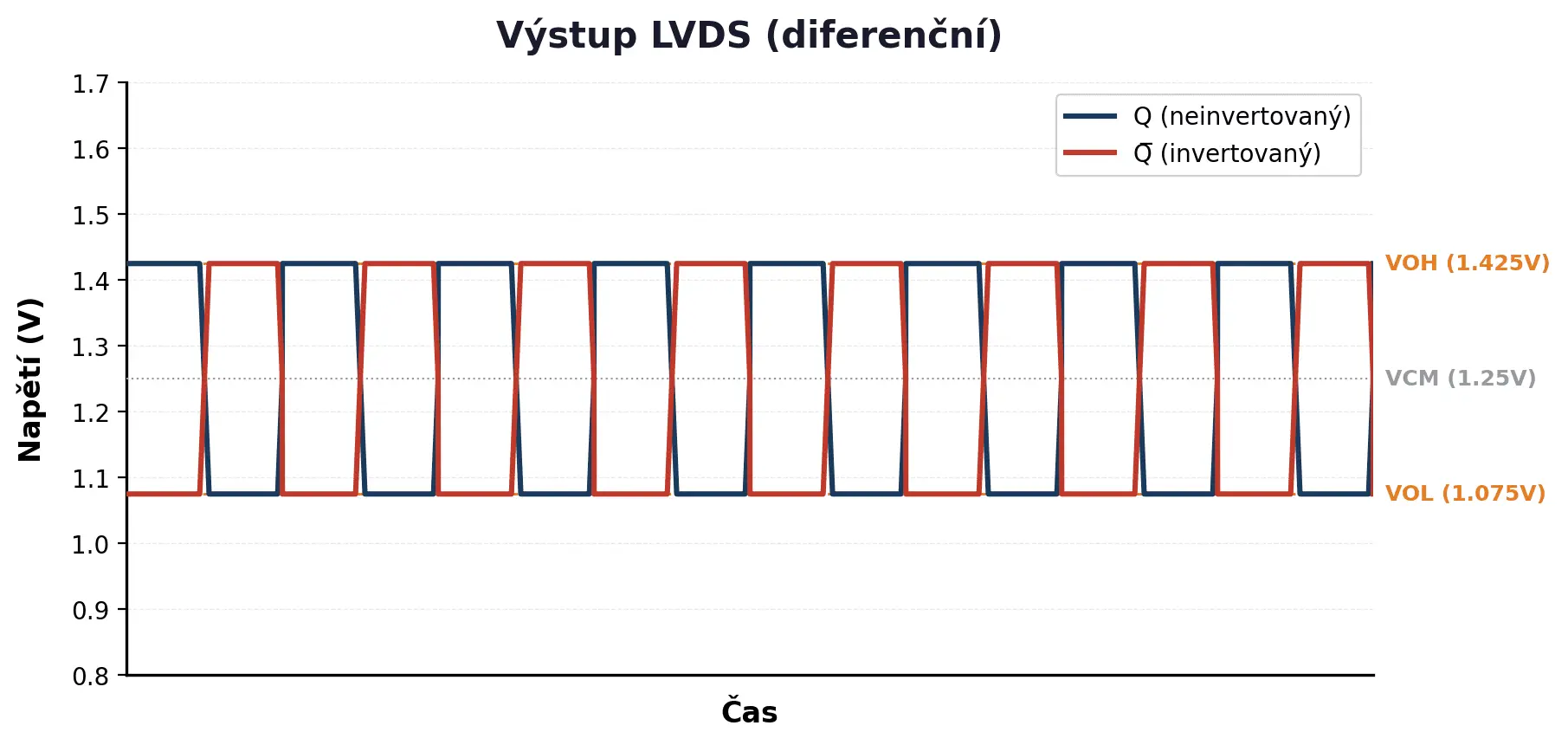

3.6 LVDS

Obr. 6: Výstup LVDS – diferenční signál s pouhými 350 mV zdvihu kolem souhlasné úrovně 1,25 V

LVDS se vyznačuje obzvláště nízkým diferenčním napěťovým zdvihem pouhých 350 mV. Souhlasná úroveň leží při 1,25 V. Díky proudově řízenému budici (typicky 3,5 mA) a terminaci 100 Ω je dosažena vysoká integrita signálu při minimální spotřebě. Nízká amplituda minimalizuje elektromagnetické vyzаřování.

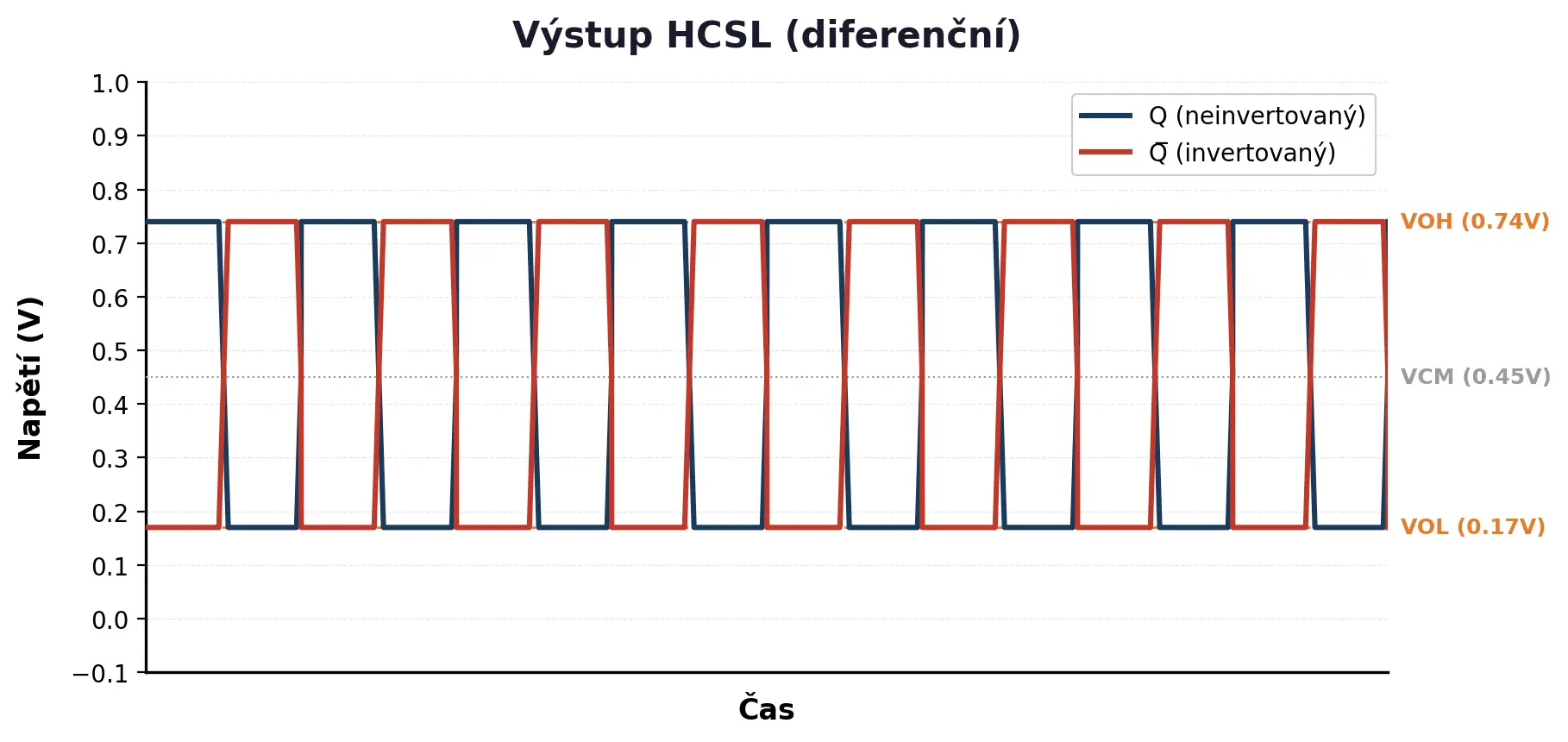

3.7 HCSL

Obr. 7: Výstup HCSL – proudově řízený diferenční signál pro referenční hodiny PCIe

HCSL pracuje s velmi nízkým napěťovým zdvihem: VOH leží typicky při 0,74 V a VOL při 0,17 V, což dává souhlasnou úroveň cca 0,45 V. Architektura proudového řízení je specificky optimalizována pro požadavky specifikace PCIe a umožňuje přesné přizpůsobení impedance prostřednictvím terminací 50 Ω k zemi.

4. Srovnání výstupních signálů

Následující tabulka shrnuje základní vlastnosti všech sedmi typů výstupů:

Typ | Typ signálu | VCC (V) | VOH/ VOL (V) | Dif. zdvih | Max. cca frekv. | Typická aplikace |

| CMOS | Single-Ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Mikrokontroléry, FPGA, obecná digitální technika |

| TTL | Single-Ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Legacy systémy, průmyslové řízení |

| Clipped Sine | Single-Ended | 1,8/2,5/3,3 | proměnlivý | - | ~200 MHz | Telekomunikace, RF aplikace |

| Sinus | Single-Ended | 3,3/5,0/12 | proměnlivý | - | >1 GHz | RF technika, měřicí přístroje, frekvenční syntéza |

| LVPECL | Diferenční | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Síťové vybavení, SONET/SDH, vysokořychlostní taktování |

| LVDS | Diferenční | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Rozhraní displejů, sériové spoje, taktování FPGA |

| HCSL | Diferenční | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | Referenční hodiny PCI Express (100 MHz) |

5. Zásadní rozdíly v detailu

5.1 Single-Ended vs. diferenční

Nejzásadnějším rozdílem mezi typy výstupů je vedení signálu. CMOS, TTL, Clipped Sine Wave a Sinus jsou signály single-ended – vztahují se ke společné zemi. LVPECL, LVDS a HCSL naproti tomu jsou diferenční signály se dvěma komplementárními vedeními. Diferenční signály nabízejí rozhodující výhody při vyšších frekvencích: potlačují souhlasné rušení, umožňují menší napěťové zdvihy a tím rychlejší přepínací časy při nižší elektromagnetické emisi.

5.2 Napěťový zdvih a odolnost proti rušení

CMOS nabízí se svým výstupem rail-to-rail největší absolutní napěťový zdvih, a tím nejlepší statickou odolnost proti rušení. TTL má kvůli asymetrickým úrovním omezenější odolnost. Diferenční standardy (LVPECL, LVDS, HCSL) kompenzují své menší napěťové zdvihy potlačením souhlasné složky diferenčního přenosu, což jim v rušeném prostředí často umožňuje spolehlivajší provoz než signálům single-ended.

5.3 Spotřeba proudu

Oscilátory CMOS ve statickém stavu spotřebovávají téměř nulový proud; spotřeba roste úměrně s frekvencí (dynamický ztrátový výkon). TTL má trvale vyšší klidovou spotřebu proudu kvůli bipolární architektuře. LVPECL vyžaduje externí terminační odpory a má nejvyšší spotřebu proudu z diferenčních standardů. LVDS je známý svou nízkou spotřebou (typicky 3,5 mA proudu budice). HCSL se z hlediska spotřeby nachází mezi LVDS a LVPECL.

5.4 Frekvenční rozsah a hlavní oblasti použití

Pro frekvence do přibližně 200 MHz jsou ve většině případů první volbou CMOS oscilátory díky své všestrannosti, jednoduchému návrhu obvodu a široké dostupnosti. Nad přibližně 200 MHz se doporučují diferenciální výstupy. LVPECL nabízí nejvyšší frekvence (> 3 GHz) a používá se v síťových a telekomunikačních zařízeních. LVDS pokrývá široký střední rozsah a je obzvláště běžný v FPGA a zobrazovacích aplikacích. HCSL je optimalizován pro své specifické použití: referenční hodiny 100 MHz pro PCI Express.

5.5 Terminace a složitost obvodu

Výstupy CMOS a TTL zpravidla nevyžadují externí terminaci při krátkých délkách vodičů – to je činí obzvláště jednoduchými v použití. LVPECL povinně vyžaduje externí terminační odpory (typicky: Théveninova terminace k VCC–2 V nebo odpory k zemi), což zvyšuje složitost obvodu. LVDS je standardně terminován diferenčním odporem 100 Ω u přijímače. HCSL používá odpory 50 Ω k zemi na každém výstupu.

6. Překmity u výstupních signálů oscilátorů

6.1 Co jsou překmity?

Překmit a podkmit jsou krátkodobé napěťové špičky, ke kterým dochází během rychlých spínacích operací. Na náběžné hraně napětí krátce překročí VCC (překmit), zatímco na sestupné hraně mírně klesne pod GND (nedokmit). Tyto špičky jsou často následovány tlumenými oscilacemi známými jako „zvonění“.

Příčina spočívá v kombinaci velmi strmých přepínacích hran výstupního budice a parazitických indukčností a kapacit vodiče, pouzdra a zátěžové kapacity. Fyzikálně vzniká rezonanční obvod z indukčnosti vedení a vstupní kapacity přijímače. Čím strmější přepínací hrana a čím delší vodič, tím výraznější překmit.

Obr. 8: Výstupní signál CMOS s překmity – overshoot nad VCC, undershoot pod GND a následný ringing

6.2 Proč jsou překmity problematické?

Překmity přesahující VCC nebo klesající pod GND mohou uvést ochranné ESD diody přijímacího obvodu do propustného směru a generovat tak parazitické proudy. V nejhorším případě to může vést k latch-up – neřízenému toku proudu přes parazitické tyristorové struktury v obvodu CMOS, který může zničit součástku. Silný ringing může navíc způsobit vícenásobné spouštění na hodinových vstupech, kdy napětí vícekrát překročí přepínací práh, což vede k chybnému chování systému.

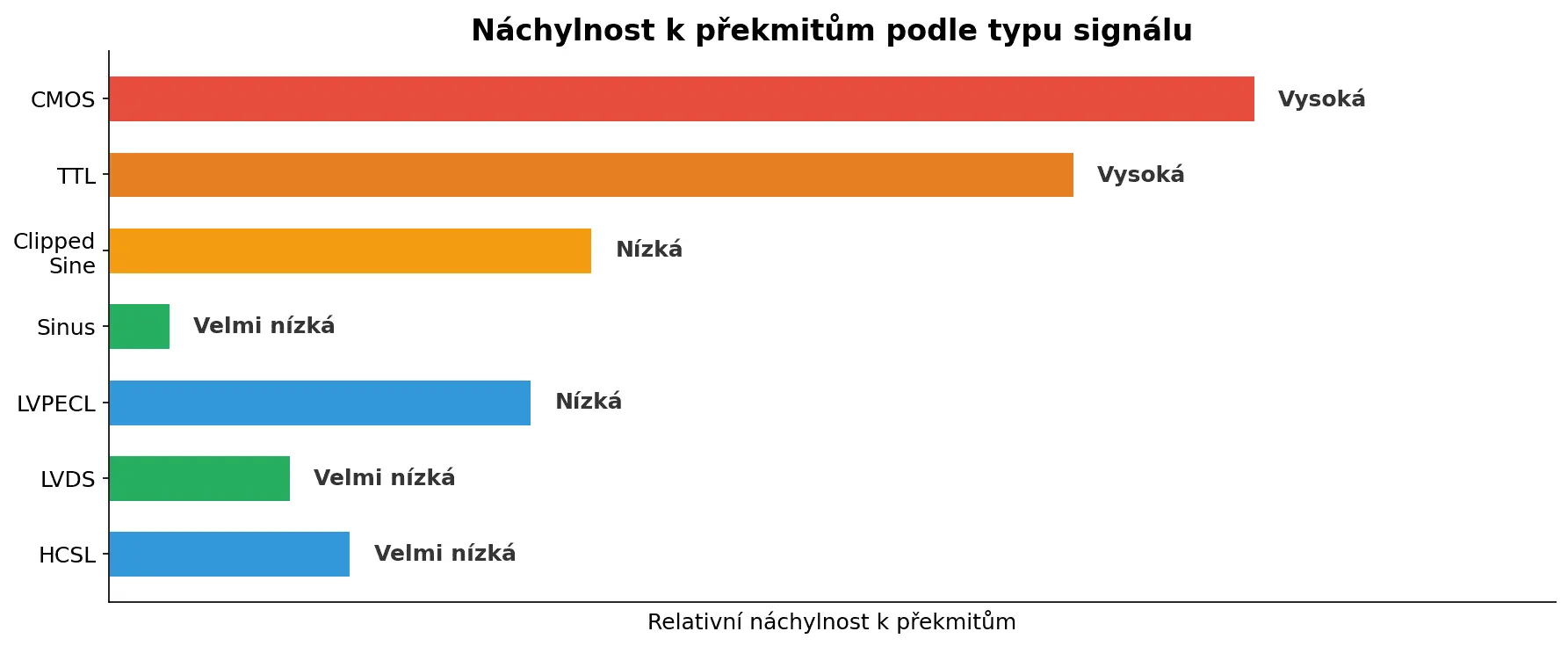

6.3 Srovnání: překmity podle typu signálu

Náchylnost k překmitům se výrazně liší mezi různými typy výstupů. Následující graf ukazuje relativní náchylnost ve srovnání:

6.4 Překmity u signálů single-ended

CMOS: Nejvíce postižený. Symetrické budice MOSFET kanálu P/N generují velmi strmé hrany, které v kombinaci s indukčnostmi vodičů způsobují výrazné překmity. Zejména u moderních nízkonapěťových oscilátorů CMOS (1,8 V) mohou být překmity vůči napájecímu napětí významné.

TTL: Rovněž náchylný, i když z poněkud jiných důvodů. Asymetrický výstupní stupeň totem-pole generuje krátký proudový impuls při náběžné hraně, kdy oba tranzistory současně vedou (cross-conduction). Typicky o něco pomalejší hrany ve srovnání s moderním CMOS problém mírně zmírňují.

Clipped Sine Wave: Výrazně méně náchylný. Omezené amplitudové špičky a srovnatelně měkké hrany produkují výrazně méně vysokofrekvenční energie, která by mohla vybudit odrazy a ringing. Oříznutí působí jako přirozené omezení amplitudy, které potlačuje překmity již v signálu.

Sinusová vlna: Prakticky imunní vůči klasickému překmitnutí. Protože signál neobsahuje žádné náhlé přechody na hranách, negeneruje se žádný širokopásmový energetický impuls, který by mohl vyvolat rezonance vedení. Impedanční nesoulad však může vést ke stojatým vlnám a odrazům, které v určitých bodech mění amplitudu signálu. To je řízeno klasickým VF zakončením (zakončení 50 Ω nebo 75 Ω).

6.5 Překmity u diferenčních signálů

LVPECL: Díky výstupnímu stupni proudového zdroje inherentně dobře potlačen. Proudové řízení přirozeně omezuje maximální strmost hran. Při nedostatečné terminaci se však mohou vyskytnout odrazy, protože LVPECL pracuje na velmi vysokých frekvencích. Správný Théveninův nebo emitorový sledovací obvod je zde rozhodující – nikoliv primárně kvůli překmitům, ale pro zajištění správného pracovního bodu a zabránění odrazům.

LVDS: Konstrukcě velmi robustní. Proudově řízený budic dodává konstantní proud typicky 3,5 mA do diferenční terminace 100 Ω, čímž je napěťový zdvih fyzikálně omezen. I při impedančních diskontinuitách zůstávají odrazy malé, protože nízký napěťový zdvih pouhých 350 mV poskytuje málo energie pro rušení. LVDS je jedním z nejshovivavějších standardů z hlediska integrity signálu.

HCSL: Chová se podobně jako LVDS díky architektuře založené na proudu. Velmi nízký napěťový zdvih a terminace 50 Ω k zemi zajišťují čisté přizpůsobení impedance. Ve specifikaci PCIe jsou přípustné překmity explicitně definovány a úzce tolerovány, takže oscilátory vyhovující HCSL inherentně splňují tyto požadavky.

6.6 Protiopatření pro kontrolu překmitů

Nejúčinnějším opatřením u signálů single-ended (zejména CMOS a TTL) je sériový odpor přímo na výstupu oscilátoru, typicky v rozsahu 22 až 47 Ω. Tento odpor tvoří spolu s impedancí vodiče napěťový dělič, který tlumí hranu a absorbuje odrazy. Optimální hodnota vyplývá z rozdílu mezi impedancí vodiče a výstupní impedancí budice.

Kromě toho pomáhají krátké vodiče s kontrolovanou impedancí, minimalizace prokovení (via) na hodinovém vedení, souvislá zemní plocha pod signálovým vedením a dostatečné odvažovací kondenzátory v blízkosti oscilátoru (typicky 100 nF keramických plus 10 µF). Někteří výrobci oscilátorů CMOS navíc nabízejí modely s kontrolovanou strmostí hran (Slew Rate Control), které problém zmírňují již v budici.

U diferenčních signálů (LVPECL, LVDS, HCSL) je správná terminace v souladu se specifikací nejdůležitějším opatřením. Kromě toho by obě vedení diferenčního páru měla být vždy vedena se stejnou délkou a těsnou vazbou, aby se minimalizoval skew (rozdíly doby šíření) a zachovalo potlačení souhlasné složky.

7. Pomoc při rozhodování

Volba správného typu výstupu závisí v zásadě na čtyřech faktorech: požadované hodinové frekvenci, logické rodině přijímače, dostupném výkonovém rozpočtu a požadavcích na integritu signálu.

Případ použití | Doporučení |

| Obecná digitální technika, µC, FPGA-I/O (do ~200 MHz) | CMOS – Nejjednodušší a nejlevnější řešení, rail-to-rail, nejširší dostupnost, flexibilní napájecí napětí (1,8–5,0 V) |

| Legacy 5V systémy, průmyslové řízení | TTL – Přímo kompatibilní se staršími 5V logickými rodinami; stále častěji nahrazován CMOS s 5V napájením |

| RF aplikace, obvody s transformátorem | Clipped Sine Wave nebo Sinus – Nižší obsah harmonických snižuje problémy EMC a umožňuje přesnou frekvenční syntézu |

| Vysokorychlostní síťová zařízení (>622 MHz) | LVPECL – Nejvyšší přepínací rychlost, ideální pro SONET/SDH, Ethernet-PHY a backplane hodiny |

| Taktování FPGA, sériový přenos dat, rozhraní displejů | LVDS – Optimální kompromis mezi rychlostí, spotřebou a chováním EMC |

| Referenční hodiny PCI Express | HCSL – Jediný hodinový standard specifikovaný PCI-SIG pro systémy PCIe |